Choć przez ostatnie 11 lat w świecie produkcji procesorów zmieniło się sporo i dzięki kolejnym innowacjom w naszych komputerach i smartfonach obecnie znajdują się układy wyprodukowane w procesie klasy 5 lub 4 nm, to przez ten czas ogólne założenia dotyczące tego, jak powinien wyglądać pojedynczy tranzystor, pozostały relatywnie niezmienione. Jednak w najnowszych procesach technologicznych klasy 3 i 2 nm konieczne stało się wysłanie służącym nam przez ponad dekadę tranzystorów finFET na zasłużoną emeryturą, ponieważ nie da się ich już bardziej pomniejszać przy zachowaniu niezbędnych parametrów elektrycznych. Co dalej? W praktyce przekonamy się o tym już niedługo.

- Od ponad dziesięciu lat standardem jest budowanie zaawansowanych mikroprocesorów z tranzystorów finFET, ale nadszedł czas na zmianę

- Już niedługo będzie możliwa komercyjna produkcja układów z tranzystorami GAAfet, które powinny wystarczyć na kilka kolejnych generacji procesów

- Pracę nad nimi prowadzi Intel, Samsung i TSMC i firmy te planują udostępnić klientom ich rezultaty w swoich procesach klasy 3 lub 2 nm.

Dlaczego potrzebujemy coraz mniejszych tranzystorów?

Zacznijmy od tego, dlaczego w ogóle potrzebujemy zmniejszać tranzystory i skąd się bierze ta bardzo kosztowa pogoń za znalezieniem sposobów na budowanie półprzewodnikowych układów z coraz mniejszych klocków. Powodów znalazłoby się więcej, ale skupimy się na trzech z nich.

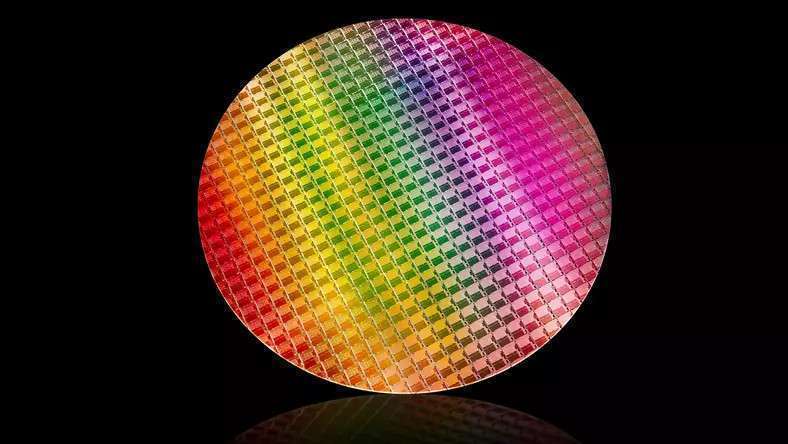

Po pierwsze, problemem jest przepustowość sprzętu i dostępność mogących go wykorzystać zasobów ludzkich. Mikroprocesory od lat powstają na krzemowych waflach, zazwyczaj o średnicy 300 mm. Wafle te są obrabiane przez bardzo zaawansowane maszyny w gigantycznych i bardzo drogich fabrykach (koszt ich budowy idzie w miliardy dolarów), a do projektowania układów, a także budowy i obsługi tych fabryk potrzebny jest wykwalifikowany personel. Na dodatek, fabryki tego typu nie tylko są nieprzyzwoicie drogie w budowie i utrzymaniu, ale też nie mogą powstać byle gdzie – w grę wchodzą tylko rejony o minimalnej aktywności sejsmicznej, z dobrym dostępem do czystej wody i w pobliżu odpowiednich ośrodków akademickich. Nie bez znaczenia jest też geopolityka. Ale nawet jeśli ktoś miałby odpowiednie środki, miejsce i personel, to pewne maszyny niezbędne do obróbki krzemowych wafli tworzy tylko jedna holenderska firma (ASML), w której na realizację zamówienia trzeba poczekać około dwóch lat.

Inaczej mówiąc, jako ludzkość możemy obrobić jedynie pewną ograniczoną liczbę krzemowych wafli, a jej zwiększenie jest bardzo, bardzo trudne (co świetnie pokazały czasy pandemii). To oznacza, że jedynym sposobem na zwiększenie liczby wyprodukowanych półprzewodników jest upchnięcie większej ich liczby na dostępnych nam krzemowych waflach. Drugą stroną tego medalu są klienci, którzy nie mogą sobie pozwolić na rozbudowanie już istniejących lub wybudowanie nowych centrów danych, a potrzebują coraz większej mocy obliczeniowej. Czyli tak jak ze strony producentów półprzewodników ograniczeniem jest powierzchnia wafli krzemowych, które mogą obrobić, tak po stronie odbiorców ograniczeniem jest powierzchnia centrów danych, w których muszą upchnąć niezbędną im moc obliczeniową.

Po drugie, w grę wchodzą pieniądze. Choć obróbka wafli krzemowych za pomocą najnowocześniejszych procesów staje się coraz droższa, to koszt wyprodukowania pojedynczego tranzystora nadal maleje wraz z jego rozmiarem (choć zdecydowanie nie w takim stopniu, jak kilkanaście lat temu). Czyli jeśli ktoś potrzebuje wykonać konkretną pracę w określonym czasie i potrzebuje do tego pewnej liczby tranzystorów, to dzięki ich zmniejszaniu może to zrobić taniej.

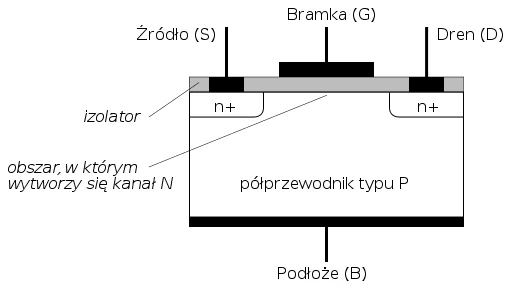

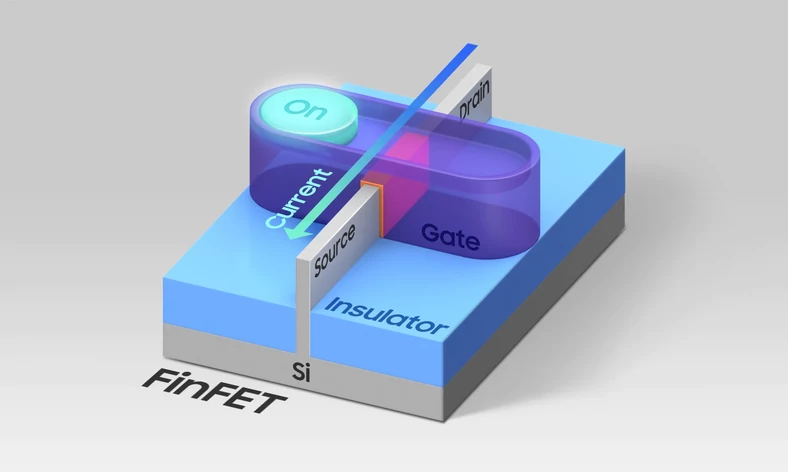

Po trzecie, w grę wchodzi użycie prądu przez pojedynczy tranzystor i szybkość jego przełączania. W bardzo dużym uproszeniu i w kontekście mikroprocesorów tranzystor to urządzenie, w którym bramka blokuje lub zezwala na przepływ prądu z punktu A do punktu B (między źródłem a drenem) poprzez tak zwany kanał. Bramkę tranzystora można sobie wyobrazić jako bramkę na autostradzie: tak jak szlaban bramki autostradowej nie otworzy się i nie zezwoli na przejazd, dopóki się nie zapłaci wymaganej kwoty, tak bramka tranzystora nie „otworzy się” i nie umożliwi przepływu prądu, dopóki nie przyłoży się do niej odpowiedniego napięcia. Gdy prąd z punktu A do punktu B płynie, to mamy 1; gdy nie płynie, to mamy 0.

Idąc dalej tropem transportowej analogii, tak jak na autostradowej bramce zależy nam na tym, aby płatność i otwieranie szlabanu zabierały jak najmniej czasu, aby nie ustawiały się kolejki, tak samo zależy nam na tym, aby bramka tranzystora „otwierała” się i „zamykała” jak najszybciej, bo wtedy może wysłać więcej zer i jedynek w jednostce czasu. Tak się składa, że mniejsze tranzystory można przełączać szybciej. Wynika to z tego, że układ kanału i bramki tworzy w praktyce kondensator, który trzeba naładować, zanim bramka umożliwi przepływ prądu z punktu A do B. Im mniejszy tranzystor, tym mniej czasu i energii trzeba zużyć na to ładowanie, a to ma bezpośrednie przełożenie na możliwe do osiągnięcia taktowanie procesora i zużycie energii. Oprócz tego, im mniejszy tranzystor, tym krótszy kanał, czyli droga, którą muszą pokonać elektrony, co oznacza, że bramka musi być otwarta krócej, aby przekazać sygnał. Przynajmniej w teorii.

Pojawiają się problemy

Do pewnego czasu miniaturyzacja tranzystorów szła sprawnie i przynosiła przewidywalne rezultaty. Co prawda po drodze trzeba było zmienić materiały, z których jest tworzona elektroda bramki (z polikrzemu na metal) i warstwa oddzielająca ją od kanału (z dwutlenku krzemu na materiał high-κ), aby poprawić właściwości elektryczne tranzystora i powstrzymać tunelowanie kwantowe elektronów przez coraz cieńszą warstwę izolacyjną, ale były to względnie proste modyfikacje. Prawdziwe problemy zaczęły się po dojściu do procesów klasy 2x i 1x nm.

Wtedy kanał stał się na tyle krótki, że pewne zjawiska, które wcześniej można było zignorować lub nie występowały, zaczęły mieć coraz większy wpływ na pracę i właściwości tranzystora. Z ich powodu bramka traciła pełną kontrolę nad sytuacją i tranzystor mógł włączać się i wyłączać w niewłaściwym momencie. Zaczęły się też pojawiać problemy z szybkością i ilością nośników prądu, które można było przesłać. Potrzebne stało się całkowite przeprojektowanie półprzewodnikowych tranzystorów.

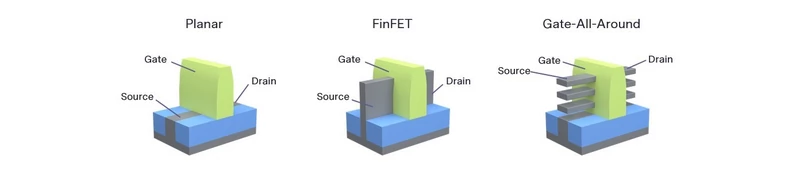

W tranzystorze idealnym kanał jest okrągłym przewodem otoczonym bramką, bo wtedy bramka działa najefektywniej. Jednak przez wiele lat tranzystory planarne mikroprocesorów miały bramkę ułożoną nad kanałem – tak było prościej, taniej i długo działało to wystarczająco dobrze. W wyniku wspomnianych przed chwilą problemów zaczęto eksplorować rozwiązania, w których bramka ma kontakt z kanałem nie tylko z góry. Wszyscy wiedzieli, jak wygląda ideał, do którego trzeba dążyć, ale początkowo był on nieosiągalny.

Na ratunek przychodzą tranzystory finFET

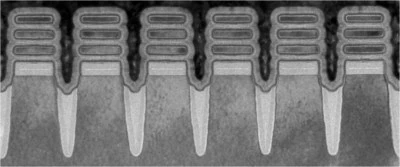

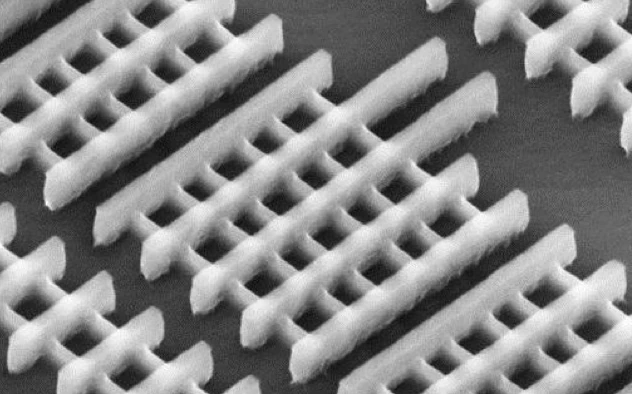

Jako pierwszy tranzystory nowej generacji wdrożył do swoich produktów Intel. W procesie Intela klasy 22 nm pojawiły się tranzystory Tri-gate, w których kanał nie jest elementem krzemowego podłoża, a wystaje z niego i jest „objęty” bramką, która ma z nim kontakt z trzech stron (lub dwóch, bo tranzystory mogą nie mieć prostokątnego przekroju, a trójkątny).

Oprócz tego, że bramka ma dzięki temu większą kontrolę nad kanałem, to ilość prądu płynącego przez tranzystor można regulować zmianą wysokości, a nie szerokości kanału i bramki, dzięki czemu zajmuje on mniej miejsca na krzemowym waflu. Dren i kanał, w zależności od potrzeb, mogą być połączone więcej niż jednym pionowym kanałem. Rozwiązanie to okazało się bardzo udane i różnego rodzaju tranzystory finFET zadomowiły się w konkurencyjnych procesach technologicznych od klasy 14/16 nm wzwyż.

„finy” też przestały wystarczać

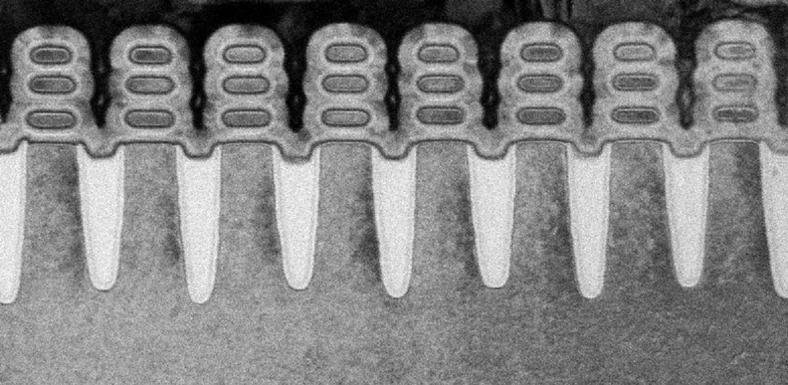

Tranzystory finFET służą nam aż dotąd, ale okazuje się, że ten styl tranzystorów nie jest wystarczający, aby opracować procesy klasy 2/3 nm i nowsze. Inżynierowie znowu wrócili do przyglądania się ideałowi tranzystora i zaczęli zastanawiać się, jak to zrobić, aby bramka całkowicie otaczała kanał. O ile sama koncepcja jest dość prosta i znana od dawna, to problemem od zawsze było to, jak wprowadzić ją w życie. Eksperymenty przyniosły pierwsze efekty w 2017 roku, gdy działającymi tranzystorami GAAfet (GAA = Gate-All-Around = bramka dookoła (w domyśle – kanału)) pochwalili się współpracujący ze sobą inżynierowie IBM, Samsunga i Global Foundries.

Kanał został w nich zbudowany z równoległych, umieszczonych jeden nad drugim nanoarkuszy. Jednak od stworzenia czegoś w laboratorium do wymyślenia, jak coś produkować na masową skalę przy zachowaniu realistycznych kosztów, to dwie zupełnie inne sprawy.

Wszyscy trzej producenci najbardziej zaawansowanych półprzewodników pracowali nad tym przez wiele lat. Samsung swoje tranzystory GAAfet nazywa MBCFET i wprowadzi je jeszcze w tym lub na początku przyszłego roku w procesie 3 nm. Intel nazywa je RibbonFET i chce je stosować w swoim procesie 20A (2 nm) w 2024 roku. A TSMC nie bawi się w wymyślne nazwy i planuje zastosować tranzystory z nanoarkuszami w swoim procesie N2 dopiero w 2025 roku. Samsung zdaje się mieć sporą przewagę, ale na razie trudno przewidzieć, w jakim stopniu ten nowy proces będzie faktycznie używalny.

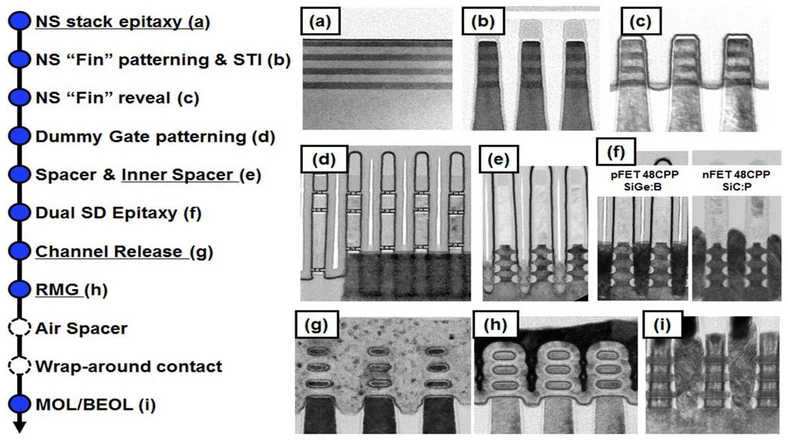

Szczegóły dotyczące tego, jak dokładnie firmy te będą tworzyć swoje tranzystory nowej generacji, trochę się różnią, ale ogólne założenia i wyzwania są bardzo podobne. Wszystko zaczyna się od naprzemiennego ułożenia na krzemowym waflu warstw germanku krzemu i krzemu. Par warstw ostatecznie jest tyle, ile nanoarkuszy ma mieć tranzystor. Później w wyniku procesów litograficznych, chemicznych i mechanicznych na waflu powstaje szachownica warstwowych struktur o długości i szerokości zbliżonej do docelowej długości i szerokości kanału tranzystora. Potem na końcach kanału tworzone są elektrody źródła i drenu. Gdy są gotowe, za pomocą procesów chemicznych ze struktury kanałów są usuwane warstwy z germanku krzemu i warstwy krzemowych nanoarkuszy są podtrzymywane jedynie przez dobudowane do nich przed chwilą elektrody. Następnie dookoła elementów kanału jest nanoszona bardzo cienka warstwa izolacyjna (ma ona grubość liczoną w pojedynczych atomach) i na koniec jest tworzona metalowa elektroda bramki.

Przez lata ogromnym wyzwaniem było dokładne pozbycie się tymczasowych warstw SiGe spomiędzy nanoarkuszy, które przy okazji nie erodowałoby powierzchni kanału – wszelkie pozostałości i nierówności w tworach o tak małej skali są niedopuszczalne, jeśli układ ma działać przewidywalnie i niezawodnie. Problematyczne jest też precyzyjne nanoszenie izolatora na spodnią stronę nanoarkuszy i dokładnie wypełnienie przerw między nimi metalem bramki. A gdy już powstały efektywne metody radzenia sobie z tym wszystkim i dokładnie dobrano wszystkie używane materiały, potrzebne okazały się zupełnie nowe metody inspekcji gotowych tranzystorów, które są w stanie wykryć defekty w niewidocznych miejscach.

Jak widać, nie ma nic dziwnego w tym, że na tranzystory GAA trzeba czekać aż tyle czasu. Jednak potencjalne korzyści są bardzo duże – nie dość, że dzięki otoczeniu kanału bramką będzie możliwe dalsze skracanie kanału (choć tutaj możliwości miniaturyzacji są coraz skromniejsze), to – co ważniejsze – kolejne elementy kanału są ustawiane w pionie, a nie na płaszczyźnie poziomej (tranzystory finFET zazwyczaj mają więcej niż jedno żebro), dzięki czemu końcowy tranzystor może mieć znacznie mniejszą powierzchnię przy zachowaniu zbliżonych właściwości elektrycznych.

Opisana tu zmiana geometrii tranzystorów połączona z przejściem w maszynach EUV na nowocześniejszą optykę o wyższej aperturze liczbowej powinna dać nam jeszcze kilka generacji coraz gęstszych i sprawniejszych procesów technologicznych. Co dalej? Na razie naprawdę trudno powiedzieć, ale będzie potrzebna jeszcze większa rewolucja, być może związana z zastąpieniem wysłużonego krzemu jakimś innym materiałem. Może nanorurki grafenowe po kilkudziesięciu latach w końcu przestaną być materiałem przyszłości, a staną się materiałem teraźniejszości? Nie byłoby też dziwne, gdyby w międzyczasie w wyniku rosnących kosztów i poziomu trudności opracowywania kolejnych technologii z wyścigu obecnej wielkiej trójki wypadłby któryś z graczy albo nastąpiłaby jakaś spektakularna fuzja. Jakkolwiek by było, możemy się spodziewać, że świat półprzewodników jeszcze nie raz nas zaskoczy i zachwyci.